RF Building Blocks

CMX940 – Low Power High Performance RF Synth with Integrated VCO

The CMX940 is a low-power high performance Fractional-N PLL with fully-integrated wideband VCO and programmable output divider, generating RF signals over a continuous frequency range of 49 MHz to 2040 MHz.

It has two level-controlled single-ended RF outputs to support Tx and Rx sub-systems. A highly-configurable near noiseless clock multiplier can be used to minimise close-in phase noise and mitigate integer and fractional boundary spurious. The chip configuration is controlled by an SPI-compatible C-BUS serial interface.

Available in a 7 x 7 mm LGA-48 package, the CMX940 reduces component count and PCB board area, requiring only external loop filter and clock reference to provide a complete and very compact RF synthesizer solution.

Low operating voltage and low power consumption make it the perfect choice for a wide variety of portable and battery powered wireless applications, including digital narrowband two-way radio equipment compliant with ETSI PMR co-existence standards applicable under the Radio Equipment Directive.

Devices are available through our Distributor Network.

Features

- RF output frequency 49 – 2040 MHz

- Low current consumption 23 – 64 mA

- Supply voltage 3.0 – 3.6 V

- Low 1 Hz normalised PLL noise floor of -225 dBc/Hz

- Typical phase noise -122 dBc/Hz, 10 kHz offset at 520 MHz

- Dual programmable RF outputs

- Low noise VCO -141 dBc/Hz, 1 MHz offset at 520 MHz

- Automatic VCO selection and calibration

- 16 and 24-bit fractional-N PLL modes

- Digital lock detect

- High comparison frequency up to 120 MHz

- Very fast frequency switching <50 µs

- Low level of spurious products -75 dBc (typ.)

Applications

- PMR / LMR (including ETSI compliant radios)

- Public Safety Radio

- Wireless Data Modem

- GNSS RTK

- Wireless Microphone

- Marine Radio

- General Purpose RF / IF

Power Supply Requirement

- 3.0 – 3.6 V

Design Resources

Q: I wish to use the EV9400 Evaluation Kit to determine the lowest noise spur free setup for the CMX940 RF Synth IC. On your website there is an application note that describes an example Octave based script that determines the optimal minimal spur, low noise setup. However, it assumes that the EV9400 is unmodified and that the CMX940 reference MCLK is 38.4MHz. I wish to test the CMX940 with a different reference clock. What can I do?

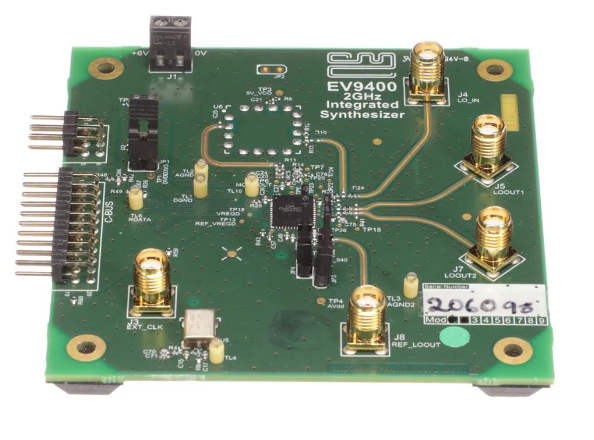

A: The “CMX940 Spur Avoidance Algorithm” Application note has been developed to be used with an unmodified EV9400 evaluation kit, which by default uses a 38.4MHz reference clock, MCLK. However, the EV9400 supports alternative reference frequencies via connector J3, “EXT_CLK” if desired. CML would therefore suggest that CML Technical Support is contacted should an alternative MCLK be used as the spur avoidance algorithm (and related “C” code) will require minor modification to support an alternative reference clock

PE0003 |

The PE0003 Evaluation Kit Interface Card is a global interface system for use with evaluation kits for CML’s new generation ICs, including FirmASIC™ based products. This greatly simplifies the approach to the evaluation and design-in process. | Link to: PE0003_Product_Page PE0003 Driver – Windows should automatically load the correct driver when the PE0003 is connected via USB and powered on. If the driver fails to load then this can be downloaded from the PE0003 page above. |

| EV9400

|

The EV9400 Evaluation Kit is designed to assist in the evaluation and application development of the CMX940.

Documents

|

EV9400 GUIA GUI for the PE0003 that provides an automated visual design tool for the EV9400. The tool allows the user to interactively develop PLL settings for the EV9400 and export those settings or import settings from another source such as the Octave-based PLL Simulation tool. A spur avoidance algorithm allows a designer to rapidly develop a library of device settings for their project. Calibration values can be captured and re-written to allow rapid channel switching with extremely fast lock times for evaluation in TDMA settings. Version 1.3 –Download |

Knowledge BaseEV9400 DWG. A higher resolution schematic for the Evaluation Kit EV9400, MOD state 2 – Download EV9400 BOM. Bill of materials for the Evaluation Kit EV9400 Rev D, MOD state 2 – Download PCB Design Files. Rev D – Download CMX940 PLL Simulation Tool. For calculating the phase noise and PLL settings in Octave. The PC GUI tool provides an interactive environment using the same method for deriving the PLL settings with spur avoidance – Download EV9400 Overlays. A hi-resolution image set for the top and bottom layer component overlay of the EV9400 Rev D, Mod State 2 – Download |

CMX940 / LMX2571 Performance Comparison

An application note that compares the key performance parameters of two Fractional-N PLLs with integrated VCOs - The CMX940 Low Power High Performance RF Synthesizer from CML Microcircuits, and the LMX2571 Low Power High-Performance RF Synthesizer from Texas Instruments.

CMX940 PLL Fast Tuning Method

An application note that describes the programming necessary to achieve fast locking of the CMX940’s synthesizers without the use of an internal calibration process. This method reduces the setup time for achieving lock and is particularly important for applications such as frequency hopping.

CMX940 Spur Avoidance Algorithm

An application note that describes how to avoid problematic spurs that can occur at certain frac-N synthesizer operating frequencies.

CMX940 Spur Avoidance Calculator

CMX940 Spur Avoidance Calculator C Code and Instructions. The C source files, and instruction guide that describe how to build and run the CMX940 Spur Avoidance Calculator Project, using the CML EC0003 C development environment and the EV9400 Evaluation and PE0003 Universal Interface Cards.