# CMX7241/CMX7341 PMR Common Platform Processor

# 7241/7341FI-4.x: APCO P25 and Analogue PMR Processor

D/7241\_7341\_FI4.x/1 May 2017

#### **DATASHEET**

**Advance Information**

#### **Features**

- Auto detect of Digital and Analogue Receive

- Digital PMR Functions:

APCO P25 conventional:

Air Interface Physical Layer (layer 1)

C4FM modulation / demodulation

Bit and symbol definition

$Frequency\ and\ symbol\ synchronisation$

Transmission burst building and splitting

- Tx Sequencer

- Analogue PMR EN 300 086 / TIA 603D:

Voice processing

De-emphasis / pre-emphasis

Tx Limiter and splatter filter

Voice scrambler

Voice compander

CTCSS and DCS generation and detection

Support for external CTCSS and DCS

Selcall generation and detection

DTMF generation and detection

1200/2400 bps FFSK modem (MPT1327 compatible)

#### **Additional Features**

- 2 Auxiliary ADCs (4 Multiplexed Inputs)

- 4 Auxiliary DACs

- 2 Auxiliary System Clock Outputs

- Tx Outputs for Two-point or I/Q Modulation

- Rx Inputs for Limiter/Discriminator or CMX994 Direct Conversion (I/Q) Receiver

- C-BUS serial interface to CMX994/A/E Direct Conversion Receiver

- Voice Codec supports external vocoders (SPI/PCM/I<sup>2</sup>S compatible e.g. IMBE)

- C-BUS Serial Interface to Host micro

- Flexible Powersave Modes

- Low-power (3.3V) Operation

- Dedicated hardware reset pin

- Single-ended inputs (CMX7241)

- Differential inputs (CMX7341)

- Available in LQFP or VQFN Packages (CMX7341 VQFN only)

# **Applications**

- Multi-mode PMR radio

- FDMA digital PMR

- Analogue PMR

## 1 Brief Description

The 7241/7341FI-4.x Function Image™ (FI) implements a half-duplex C4FM modem and a large proportion of the C4FM Air Interface physical layer. In addition, the FI also supports Analogue FM voice modes with flexible signalling options. In conjunction with a suitable host and an RF transceiver, a compact, low-cost, low-power digital PMR radio conforming to C4FM digital radio standards and Analogue EN 300 086 / TIA 603D can be realised. The FI analyses incoming traffic, detects the modulation type and switches to the associated operating mode. This ensures that dual mode, analogue/digital PMR operation can be achieved on a single radio platform without the need to re-configure hardware or software by loading alternative FIs.

The CMX7241 and CMX7341 when loaded with the FI are identical in functionality; the only difference between the two devices is in the input stage: the CMX7241 has single-ended inputs and the CMX7341 is a differential input version.

The embedded functionality of the 7241/7341FI-4.x minimises host microcontroller interactions enabling the lowest operating power and therefore the longest battery life. The CMX7241/7341 can also provide audio codec functionality for vocoders under direct host control.

The in-built signalling options allow the device to be implemented into legacy Analogue FM systems making use of CTCSS / DCS sub-audio signalling, Selcall / DTMF signalling or 1200/2400 bps FFSK trunked systems using MPT1327 or custom protocols.

Both digital and analogue functionality can be active at the same time, allowing the host to auto-detect the type of signalling on the channel.

The device allows the designer to choose between a conventional limiter/discriminator receiver architecture or an I/Q-based direct conversion architecture utilising the built-in support for the CMX994 Direct Conversion Receiver.

The CMX7241 and CMX7341 utilise CML's proprietary *FirmASIC*<sup>®</sup> component technology. On-chip sub-systems are configured by a Function Image™: This is a data file that is uploaded during device initialisation and defines the device's function and feature set. The Function Image™ can be loaded automatically from an external serial memory or host microcontroller over the built-in C-BUS serial interface. The device's functions and features may be enhanced by future Function Image™ releases, facilitating in-the-field upgrades. This document refers specifically to the features provided by Function Image™ 7241/7341FI-4.0.x.x.

Other device features include two auxiliary ADCs with four selectable inputs and four auxiliary DAC interfaces (with an optional RAMDAC on the first DAC output, to facilitate transmitter power ramping).

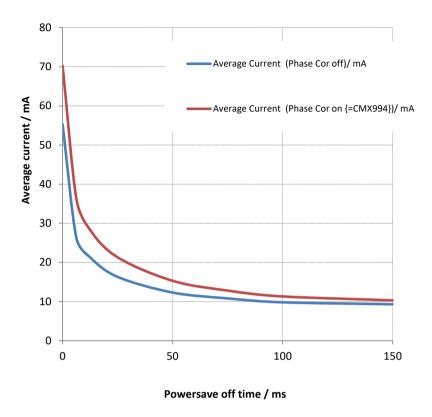

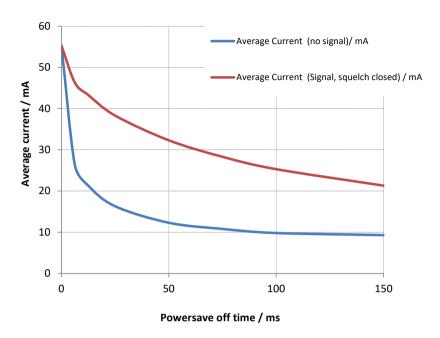

The CMX7241 and CMX7341 have flexible powersaving modes and are available in the following packages: CMX7241 (VQFN and LQFP), CMX7341 (VQFN only).

Note that text shown in pale grey indicates features that will be supported in future versions of the Function Image™.

This datasheet is the first part of a two-part document comprising datasheet and user manual: the datasheet/user manual combination can be obtained by registering your interest in this product with your local CML representative.

© 2017 CML Microsystems Plc Page 2 D/7241\_7341\_FI4.x/1

# CONTENTS

| <u>Section</u> | <u>!</u>                                                   | Page |

|----------------|------------------------------------------------------------|------|

| 1              | Brief Description                                          | 2    |

| 2              | Block Diagram                                              | 8    |

| 3              | Signal List                                                |      |

| 3.1            | Signal Definitions                                         |      |

|                |                                                            |      |

| 4              | Component and PCB Recommendations                          |      |

| 4.1            | Recommended External Components                            |      |

| 4.2            | PCB Layout Guidelines and Power Supply Decoupling          |      |

| 4.3<br>4.4     | CMX994/CMX994A/CMX994E Interface<br>Serial Port Interfaces |      |

| 4.4<br>4.5     | RESET Pin                                                  |      |

|                |                                                            |      |

| 5              | General Description                                        |      |

| 5.1            | 7241/7341FI-4 Features                                     |      |

| 5.2            | Digital Features                                           |      |

| 5.3            | Analogue Features                                          |      |

| 5.4            | Auxiliary Functions                                        |      |

| 5.5            | Interface                                                  |      |

| 5.6            | System Design                                              |      |

| 5.6.1          | General                                                    |      |

| 5.6.2          | Third-party Vocoder Support                                |      |

| 5.6.3          | Data Transfer                                              |      |

| 5.6.4          | CMX994 Connection (I/Q Mode)                               |      |

| 5.6.5          | Hardware AGC – AuxADC1 Connection                          |      |

| 5.6.6          | RSSI Measurement (I/Q Mode)                                |      |

| 5.6.7          | RSSI Measurement (LD mode)                                 |      |

| 5.7            | C4FM Modem                                                 |      |

| 5.7.1          | Modulation                                                 |      |

| 5.7.2          | Internal Data Processing                                   |      |

| 5.7.3          | Frame Sync Detection and Demodulation                      |      |

| 5.7.4          | Voice Coding                                               |      |

| 5.7.5          | Radio Performance Requirements                             |      |

| 5.8            | Audio/Voice Functions                                      |      |

| 5.8.1          | Microphone                                                 |      |

| 5.8.2          | Speaker                                                    |      |

| 5.8.3          | Modulation                                                 |      |

| 5.8.4          | Audio / Voice processing                                   |      |

| 5.8.5          | Sub-Audio Signalling                                       |      |

| 5.8.6          | In-band Signalling                                         |      |

| 6              | Detailed Descriptions                                      |      |

| 6.1            | Xtal Frequency                                             | 27   |

| 6.2            | Host Interface                                             |      |

| 6.2.1          | C-BUS Operation                                            |      |

| 6.2.2          | C-BUS FIFO operation                                       |      |

| 6.3            | Function Image™ Loading                                    |      |

| 6.3.1          | FI Loading from Host Controller                            |      |

| 6.4            | External Codec Support                                     |      |

| 6.4.1          | DVSI Vocoder Interface                                     |      |

| 6.4.2          | Support for I <sup>2</sup> S Mode                          |      |

| 6.5            | Device Control                                             | _    |

| 6.5.1          | General Notes                                              |      |

| 6.5.2          | Interrupt Operation                                        |      |

| 6.5.3          | Signal Routing                                             |      |

| 6.5.4          | Mode Control                                               |      |

| 6.5.5          | Tx Mode C4FM Raw                                           |      |

| 6.5.6          | Tx Mode PRBS                                               |      |

| 6.5.7          | Tx Mode Preamble                                           |      |

| 6.5.8          | Tx Mode Mod Set-up                                         |      |

| 6.5.9          | Tx Mode Test                                               | 35   |

| 6.5.10 | Tx Sequencer                                  | 35 |

|--------|-----------------------------------------------|----|

| 6.5.11 | Rx Mode Raw                                   | 36 |

| 6.5.12 | Rx Mode Eye                                   | 36 |

| 6.5.13 | Rx Pass-through Mode                          | 36 |

| 6.5.14 | Rx Mode with CMX994 AGC (I/Q Mode only)       | 37 |

| 6.5.15 | Rx Mode with CMX994 I/Q Cal (I/Q Mode only)   | 37 |

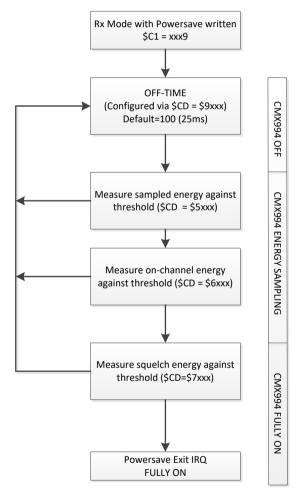

| 6.5.16 | Rx Mode with CMX994 Powersave (I/Q mode only) | 38 |

| 6.5.17 | Data Transfer                                 | 41 |

| 6.5.18 | CMX994 Pass-through                           | 42 |

| 6.6    | Analogue PMR Description                      | 42 |

| 6.6.1  | Sub-Audio Processing                          | 42 |

| 6.6.2  | Voice Processing                              | 42 |

| 6.6.3  | 300Hz HPF                                     | 42 |

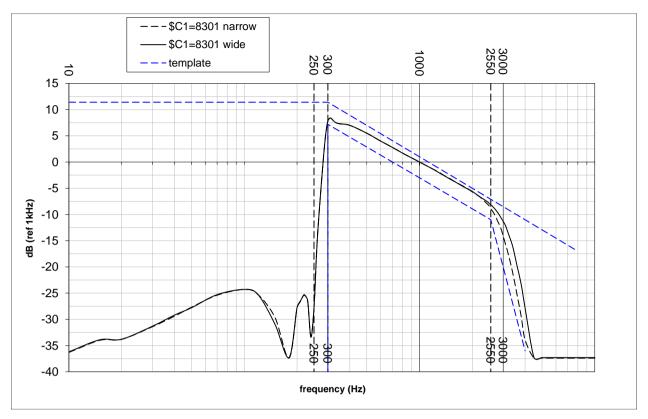

| 6.6.4  | 12.5kHz/25kHz Channel Filters                 | 43 |

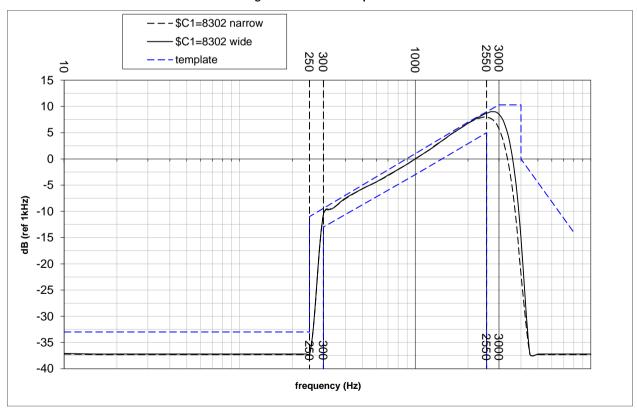

| 6.7    | FFSK Data Modem                               | 48 |

| 6.7.1  | Receiving FFSK Signals                        | 49 |

| 6.7.2  | Transmitting FFSK Signals                     |    |

| 6.8    | Selcall Signalling                            |    |

| 6.8.1  | Receiving and Decoding Selcall Tones          |    |

| 6.8.2  | Transmitting Selcall Tones                    | 51 |

| 6.8.3  | Alternative Selcall Tone Sets                 | 51 |

| 6.9    | DTMF Signalling                               | 51 |

| 6.9.1  | Reception and Decoding of DTMF                | 51 |

| 6.9.2  | Transmission of DTMF                          |    |

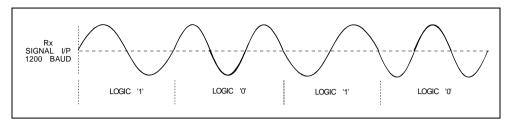

| 6.10   | Squelch Operation                             | 52 |

| 6.11   | GPIO Pin Operation                            |    |

| 6.12   | Auxiliary ADC Operation                       | 53 |

| 6.13   | Auxiliary DAC/RAMDAC Operation                |    |

| 6.14   | Digital System Clock Generators               |    |

| 6.14.1 | Main Clock Operation                          |    |

| 6.14.2 | System Clock Operation                        | 56 |

| 6.15   | Signal Level Optimisation                     |    |

| 6.15.1 | Transmit Path Levels                          |    |

| 6.15.2 | Receive Path Levels                           |    |

| 6.16   | Tx Spectrum Plots                             | 58 |

| 7      | Performance Characteristics                   | 59 |

| 7.1    | Electrical Performance                        |    |

| 7.1.1  | Absolute Maximum Ratings                      | 59 |

| 7.1.2  | Operating Limits                              |    |

| 7.1.3  | Operating Characteristics                     | 61 |

| 7.1.4  | Parametric Performance                        | 66 |

| 7.2    | C-BUS Timing                                  |    |

| 7.3    | Packaging                                     | 69 |

| <u>Table</u>                                                                                        | <u>Page</u> |

|-----------------------------------------------------------------------------------------------------|-------------|

| Table 1 Definition of Power Supply and Reference Voltages                                           | 11          |

| Table 2 Recommended External Components                                                             |             |

| Table 3 Recommended External Components when using CMX994                                           | 18          |

| Table 4 Serial Port Assignments                                                                     |             |

| Table 5 CMX994 Connections                                                                          | 21          |

| Table 6 Modulation Deviation                                                                        |             |

| Table 7 Xtal/Clock Frequency Settings for Program Block 3                                           |             |

| Table 8 C-BUS FIFO Registers                                                                        |             |

| Table 9 BOOTEN Pin States                                                                           |             |

| Table 10 DVSI Vocoder Connections                                                                   |             |

| Table 11 Device Mode Selection                                                                      |             |

| Table 12 C4FM Modem Control Selection                                                               |             |

| Table 13 Analogue Mode Selection                                                                    |             |

| Table 15 Variation in Average Current Consumption with Different Powersave States / Test Conditions |             |

| Table 16 DCS Codes and Values                                                                       |             |

| Table 17 CTCSS Codes and Values                                                                     |             |

| Table 18 Data Frequencies for MPT1327 mode                                                          |             |

| Table 19 Selcall Tones                                                                              |             |

| Table 20 Alternative Selcall Tone Sets                                                              |             |

| Table 21 DTMF Tone Pairs                                                                            | _           |

| Table 22 DTFM Twist                                                                                 |             |

|                                                                                                     |             |

| Figur <u>e</u>                                                                                      | Page        |

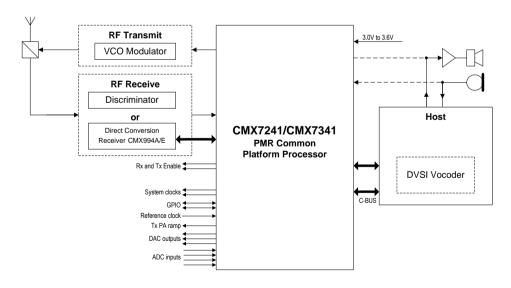

| Figure 1 CMX7241/CMX7341 Block Diagram                                                              | Q           |

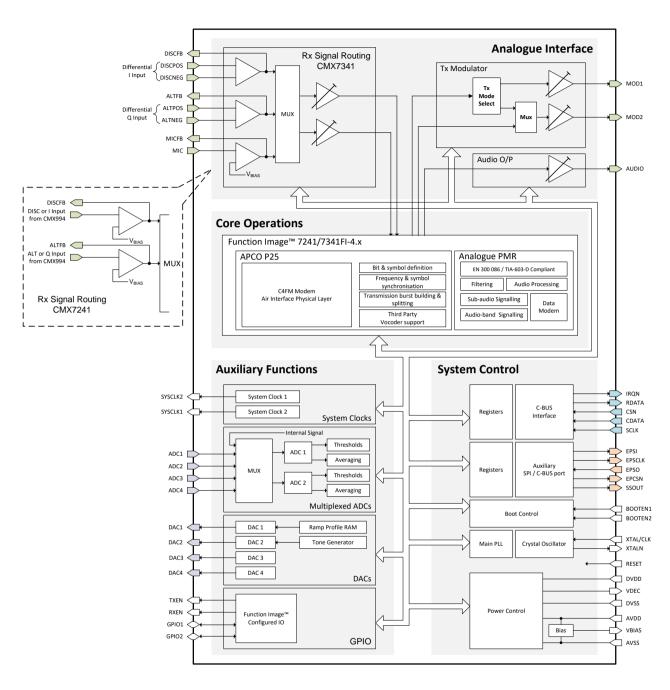

| Figure 2 CMX7241/CMX7341 Block Diagram                                                              |             |

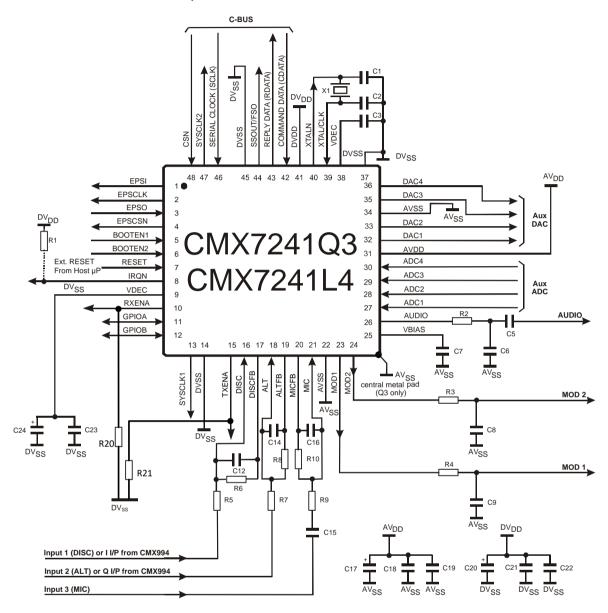

| Figure 3 CMX7341 (Q3) Recommended External Components                                               |             |

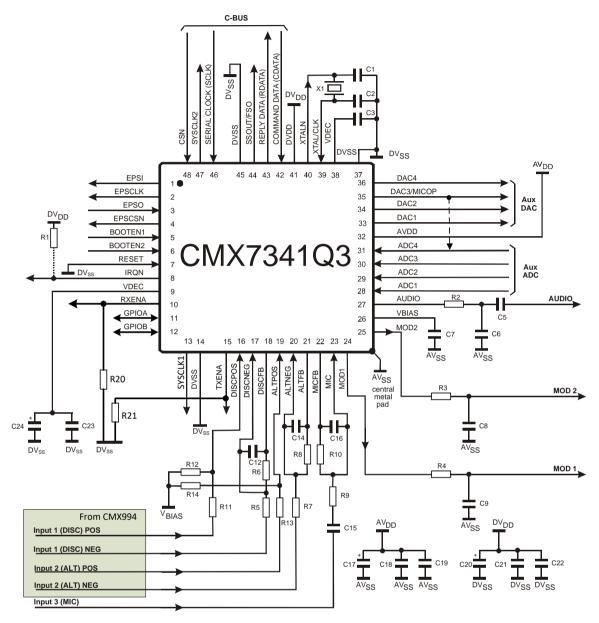

| Figure 4 CMX7241 (L4/Q3) Power Supply and Decoupling                                                |             |

| Figure 5 CMX7341 (Q3) Power Supply and De-coupling                                                  |             |

| Figure 6 CMX7241/CMX994 Interface                                                                   |             |

| Figure 7 CMX7341/CMX994 Interface                                                                   |             |

| Figure 8 DVSI Vocoder Connection                                                                    |             |

| Figure 9 CMX994 and DVSI Connection                                                                 |             |

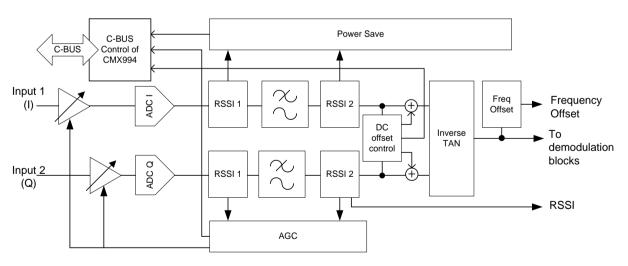

| Figure 10 RSSI in I/Q Mode                                                                          |             |

| Figure 11 C4FM PRBS Waveform (Eye Diagram)                                                          |             |

| Figure 12 C4FM Modulation Performance                                                               |             |

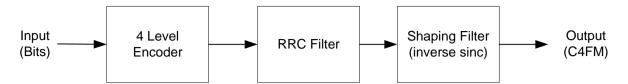

| Figure 13 C4FM Modulation Characteristics                                                           | 23          |

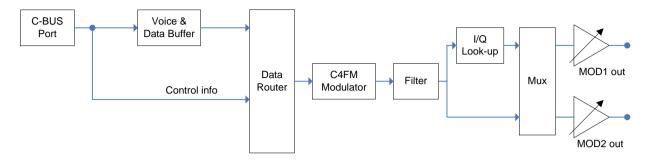

| Figure 14 Internal C4FM Data Processing Blocks                                                      | 24          |

| Figure 15 Additional Internal Data Processing in I/Q Mode                                           | 24          |

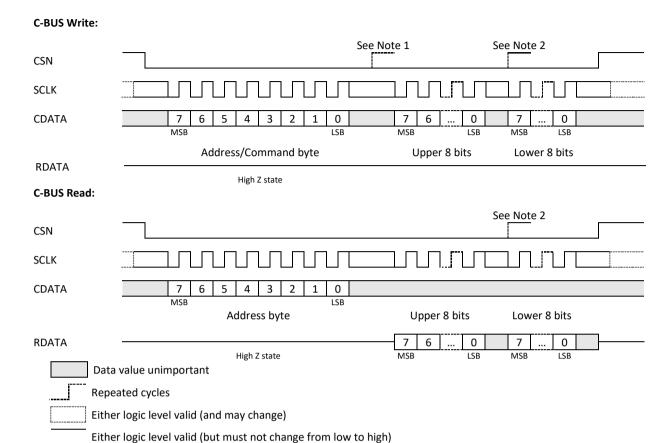

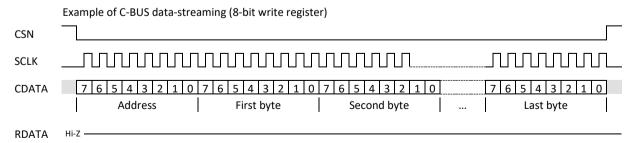

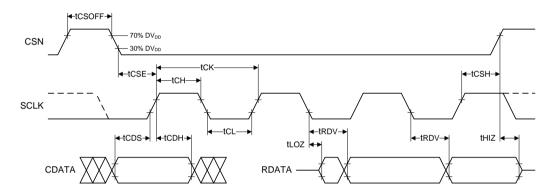

| Figure 16 C-BUS Transactions                                                                        | 28          |

| Figure 17 C-BUS Data-Streaming Operation                                                            | 29          |

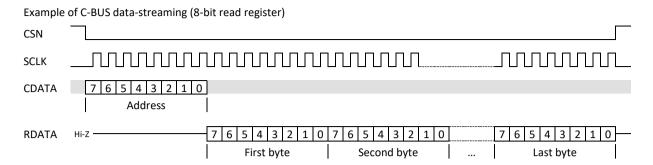

| Figure 18 FI Loading from Host                                                                      | 31          |

| Figure 19 Tx Sequencer Delay Timers                                                                 |             |

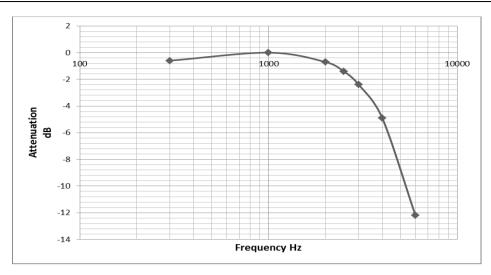

| Figure 20 Frequency Response for Rx Pass-through Mode                                               |             |

| Figure 21 Format of CMX994A/E Extended Rx Offset register (\$17)                                    |             |

| Figure 22 Format of I/Q DC calibration reporting when CMX994A/CMX994E is selected                   |             |

| Figure 23 Powersave States                                                                          |             |

| Figure 24 Effect of Powersave as a Function of "OFF" Time                                           |             |

| Figure 25 Effect of Powersave as a Function of "OFF" Time (Best and Worst Case)                     |             |

| Figure 26 Rx and Tx Level Adjustments and Routing                                                   |             |

| Figure 27 Rx Audio Response                                                                         |             |

| Figure 28 Tx Audio Response                                                                         |             |

| Figure 29 CTCSS and DCS filters                                                                     |             |

| Figure 30 Modulating Waveforms for 1200 MSK/FFSK Signals                                            |             |

| Figure 31 AuxADC IRQ Operation                                                                      |             |

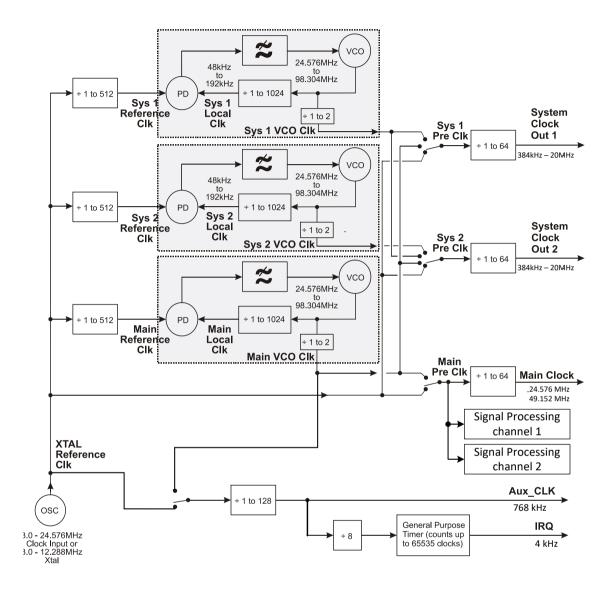

| Figure 32 Digital Clock Generation Schemes                                                          |             |

| Figure 34 By Levels (LD mode)                                                                       |             |

| Figure 34 Rx Levels (LD mode)                                                                       |             |

| Figure 35 | Tx Modulation Spectra – 4.8kbps         | .58 |

|-----------|-----------------------------------------|-----|

| _         | C-BUS Timing                            |     |

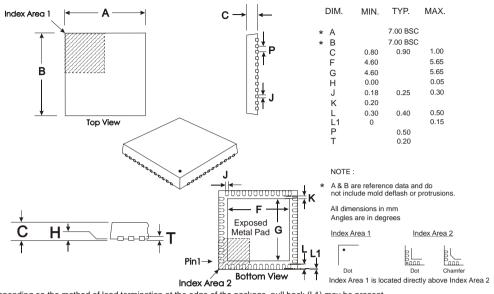

| _         | Mechanical Outline of 48-lead VQFN (Q3) |     |

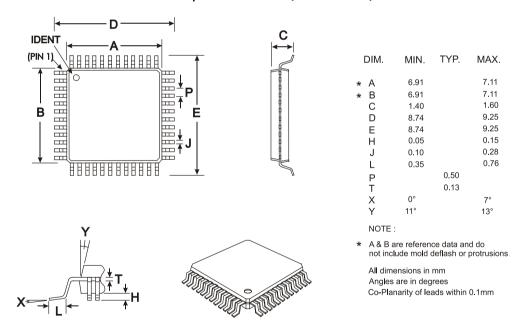

| Figure 38 | Mechanical Outline of 48-pin LQFP (L4)  | .69 |

## <u>History</u>

| Version | Version Changes                             |          |  |  |  |

|---------|---------------------------------------------|----------|--|--|--|

| 1       | First public release as Advance Information | May 2017 |  |  |  |

| Α       | Advance Draft                               | May 2017 |  |  |  |

It is recommended that you check for the latest product datasheet version from the CML website: [www.cmlmicro.com/]. This is Advance Information; changes and additions may be made to this specification. Parameters marked TBD or left blank will be included in later issues. Items that are highlighted or greyed out should be ignored. These will be clarified in later issues of this document.

# 2 Block Diagram

Figure 1 CMX7241/CMX7341 Block Diagram

# 3 Signal List

| CMX7241<br>48-pin<br>Q3/L4 | CMX7341<br>48-lead<br>Q3 | Pin<br>Name                                                                                                                                        | Туре                       | Description                                                                                                                                                                                                                                                                                             |                         |                                                 |  |

|----------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------------------------------------------------|--|

| 1                          | 1                        | 1 EPSI OP Serial Data Output                                                                                                                       |                            |                                                                                                                                                                                                                                                                                                         |                         |                                                 |  |

| 2                          | 2                        | EPSCLK                                                                                                                                             | OP                         | Serial Clock Output                                                                                                                                                                                                                                                                                     | _                       |                                                 |  |

| 3                          | 3 3 EPSO                 |                                                                                                                                                    | IP+PD                      | Serial Data Input                                                                                                                                                                                                                                                                                       | Αι                      | ixiliary SPI/C-BUS                              |  |

| 4                          | 4                        | EPCSN                                                                                                                                              | OP                         |                                                                                                                                                                                                                                                                                                         |                         |                                                 |  |

| 5                          | 5                        | BOOTEN1                                                                                                                                            | IP+PD                      | Used in conjunction with BOOTEN the bootstrap program                                                                                                                                                                                                                                                   | 2 to deter              | mine the operation of                           |  |

| 6                          | 6                        | BOOTEN2                                                                                                                                            | IP+PD                      | Used in conjunction with BOOTEN the bootstrap program                                                                                                                                                                                                                                                   | 1 to deter              | mine the operation of                           |  |

| 7                          | 7                        | RESET                                                                                                                                              | PWR                        | Dedicated reset function – activ<br>same effect as a power on reset. I                                                                                                                                                                                                                                  | _                       |                                                 |  |

| 8                          | 8                        | IRQN                                                                                                                                               | OP                         | A 'wire-ORable' output for connect<br>the Interrupt Request input of the<br>Pulled down to DV <sub>SS</sub> when active<br>high impedance when inactive. Ar                                                                                                                                             | host.<br>and is         | Host C-BUS                                      |  |

|                            |                          |                                                                                                                                                    |                            | pull-up resistor (R1) is required. Internally-generated 1.8V digital s                                                                                                                                                                                                                                  | upply volta             | age. Must be                                    |  |

|                            | _                        |                                                                                                                                                    |                            | decoupled to DV <sub>SS</sub> by capacitors r                                                                                                                                                                                                                                                           | nounted cl              | ose to the device pins.                         |  |

| 9                          | 9                        | 9 VDEC PWR No other connections allowed. If the device is to 1.8V external supply then the VDEC pin must be to the external 1.8V regulated supply. |                            |                                                                                                                                                                                                                                                                                                         |                         |                                                 |  |

| 10                         | 10                       | RXENA                                                                                                                                              |                            |                                                                                                                                                                                                                                                                                                         | = 1)                    |                                                 |  |

| 11                         | 11                       | GPIOA                                                                                                                                              | BI                         | General Purpose I/O pin                                                                                                                                                                                                                                                                                 | (,                      | ,                                               |  |

| 12                         | 12                       | GPIOB                                                                                                                                              | BI General Purpose I/O pin |                                                                                                                                                                                                                                                                                                         |                         |                                                 |  |

| 13                         | 13                       | SYSCLK1                                                                                                                                            | OP                         | OP Synthesised Digital System Clock Output 1                                                                                                                                                                                                                                                            |                         |                                                 |  |

| 14                         | 14                       | DVSS                                                                                                                                               | PWR                        | Digital ground                                                                                                                                                                                                                                                                                          | <u> </u>                |                                                 |  |

| 15                         | 15                       | TXENA                                                                                                                                              | OP                         | Tx Enable – active when in Tx mod                                                                                                                                                                                                                                                                       | de (\$C1:b1             | = 1)                                            |  |

| 16                         |                          | DISC                                                                                                                                               | IP                         | Discriminator inverting input or I i                                                                                                                                                                                                                                                                    | nput from               | CMX994                                          |  |

| 17                         |                          | DISCFB                                                                                                                                             | OP                         | Discriminator input amplifier feedback                                                                                                                                                                                                                                                                  |                         |                                                 |  |

| 18                         |                          | ALT                                                                                                                                                | IP                         | Alternate inverting input or Q inpu                                                                                                                                                                                                                                                                     | ut from CN              | 1X994                                           |  |

| 19                         |                          | ALTFB                                                                                                                                              | OP                         | Alternate input amplifier feedback                                                                                                                                                                                                                                                                      | <                       |                                                 |  |

|                            | 16                       | DISCPOS                                                                                                                                            | IP                         | Differential input1, positive and ne                                                                                                                                                                                                                                                                    | ogativo Liu             | anut from CMYQQA                                |  |

|                            | 17                       | DISCNEG                                                                                                                                            | IP                         |                                                                                                                                                                                                                                                                                                         | egative. i ii           | Tput from Civix994                              |  |

|                            | 18                       | DISCFB                                                                                                                                             | OP                         | Input1 amplifier feedback                                                                                                                                                                                                                                                                               |                         |                                                 |  |

|                            | 19                       | ALTPOS                                                                                                                                             | IP                         | Differential input2, positive and n                                                                                                                                                                                                                                                                     | egative. O              | input from CMX994                               |  |

|                            | 20                       | ALTNEG                                                                                                                                             | IP                         |                                                                                                                                                                                                                                                                                                         | J J. Q                  | ,                                               |  |

|                            | 21                       | ALTFB                                                                                                                                              | OP                         | Input2 amplifier feedback                                                                                                                                                                                                                                                                               |                         |                                                 |  |

| 20                         | 22                       | MICFB                                                                                                                                              | OP                         | Microphone input amplifier feedb                                                                                                                                                                                                                                                                        | ack                     |                                                 |  |

| 21                         | 23                       | MIC                                                                                                                                                | IP DWD                     | Microphone inverting input                                                                                                                                                                                                                                                                              |                         |                                                 |  |

| 22                         | n/c                      | AVSS<br>MOD1                                                                                                                                       | PWR                        | Analogue ground                                                                                                                                                                                                                                                                                         |                         |                                                 |  |

| 23<br>24                   | 24<br>25                 | MOD1<br>MOD2                                                                                                                                       | OP<br>OP                   | Modulator 1 output                                                                                                                                                                                                                                                                                      |                         |                                                 |  |

| 24                         | 25                       | IVIUUZ                                                                                                                                             | UP                         | Modulator 2 output                                                                                                                                                                                                                                                                                      | of approx               | AVan/2 except when                              |  |

| 25                         | 26                       | VBIAS                                                                                                                                              | ОР                         | Internally generated bias voltage of approx. AV <sub>DD</sub> /2, except v the device is in 'Powersave' mode when V <sub>BIAS</sub> will discharge to AV <sub>SS</sub> . Must be decoupled to AV <sub>SS</sub> by a capacitor mounted clos the device pins. No other connections allowed unless buffere |                         | s will discharge to itor mounted close to       |  |

| 26                         | 27                       | AUDIO                                                                                                                                              |                            |                                                                                                                                                                                                                                                                                                         |                         |                                                 |  |

| 27                         | 28                       | ADC1                                                                                                                                               | IP                         | Auxiliary ADC input 1                                                                                                                                                                                                                                                                                   | Each of th              | e two ADC blocks can                            |  |

| 28                         | 29                       | ADC2                                                                                                                                               | IP                         | Auxiliary ADC input 2                                                                                                                                                                                                                                                                                   |                         | nput signal from any                            |  |

| 29                         | 29 30 ADC3 IP Auxilia    |                                                                                                                                                    | Auxiliary ADC input 3      |                                                                                                                                                                                                                                                                                                         | ese input pins, or from |                                                 |  |

| 30                         |                          |                                                                                                                                                    | IP                         | Auxiliary ADC input 4                                                                                                                                                                                                                                                                                   |                         | ALT or DISC input pins.<br>In 6.12 for details. |  |

| CMX7241<br>48-pin<br>Q3/L4 | CMX7341<br>48-lead<br>Q3 | Pin<br>Name | Туре  | Description                                                                                                                                                                                                          |                                         |

|----------------------------|--------------------------|-------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| 31                         | 32                       | AVDD        | PWR   | Analogue +3.3V supply rail. Levels and th are proportional to this voltage. This pin ${\rm AV}_{\rm SS}$ by capacitors mounted close to the                                                                          | should be decoupled to                  |

| 32                         | 33                       | DAC1        | OP    | Auxiliary DAC output 1 / RAMDAC                                                                                                                                                                                      |                                         |

| 33                         | 34                       | DAC2        | OP    | Auxiliary DAC output 2 / Tone Generator                                                                                                                                                                              | output                                  |

| 34                         | n/c                      | AVSS        | PWR   | Analogue ground                                                                                                                                                                                                      |                                         |

| 35                         | 35                       | DAC3        | OP    | Auxiliary DAC output 3. See Note 2                                                                                                                                                                                   |                                         |

| 36                         | 36                       | DAC4        | OP    | Auxiliary DAC output 4                                                                                                                                                                                               |                                         |

| 37                         | 37                       | DVSS        | PWR   | Digital Ground                                                                                                                                                                                                       |                                         |

| 38                         | 38                       | VDEC        | PWR   | Internally generated 1.8V supply voltage. DV <sub>SS</sub> by capacitors mounted close to the No other connections allowed. If the devi 1.8V external supply, then VDEC pin must the 1.8V external regulated supply. | device pins.<br>ice is to be run from a |

| 39                         | 39                       | XTAL/CLK    | IP    | Input from the external clock source or X                                                                                                                                                                            | tal                                     |

| 40                         | 40                       | XTALN       | ОР    | NC if external clock used.  Digital +3 3V supply rail. This pin should be decoupled to DVss                                                                                                                          |                                         |

| 41                         | 41                       | DVDD        | PWR   |                                                                                                                                                                                                                      |                                         |

| 42                         | 42                       | CDATA       | IP    | Command Data input from the μC                                                                                                                                                                                       |                                         |

| 43                         | 43                       | RDATA       | TS OP | Reply Data tri-state output to the $\mu$ C (high impedance when not sending data to the $\mu$ C).                                                                                                                    | Host C-BUS                              |

| 44                         | 44                       | SSOUT       | OP    | Frame Sync for SPI Codec                                                                                                                                                                                             | Auxiliary SPI/C-BUS                     |

| 45                         | 45                       | DVSS        | PWR   | Digital ground                                                                                                                                                                                                       |                                         |

| 46                         | 46                       | SCLK        | IP    | Serial clock input from the μC                                                                                                                                                                                       | Host C-BUS                              |

| 47                         | 47                       | SYSCLK2     | OP    | Synthesised Digital System Clock 2                                                                                                                                                                                   |                                         |

| 48                         | 48                       | CSN         | IP    | Chip Select input from the μC (no internal pullup on this input)                                                                                                                                                     | Host C-BUS                              |

| Exposed<br>Metal Pad       | Exposed<br>Metal Pad     | SUBSTRATE   | ~     | The central metal pad (which is exposed be connected to analogue ground (AV <sub>SS</sub> ).  No other electrical connection is permitted.                                                                           | •                                       |

Note 1: IP = Input (+ PU/PD = internal pullup / pulldown resistor)

OP = Output

BI = Bidirectional

TS OP = 3-state Output

PWR = Power Connection

NC = No Connection - should NOT be connected to any signal.

# **Colour Definitions:**

= Aux SPI/C-BUS = Host C-BUS

= Analogue Inputs/Outputs

= ADCs/DACs

**Note 2**: In CMX7341 only, this is a dual-purpose pin which, for some FIs, may have an alternative configuration. However for FI-4, this pin ONLY functions as DAC3.

# 3.1 Signal Definitions

| Signal Name      | Pins                                                         | Usage                                                               |  |  |  |

|------------------|--------------------------------------------------------------|---------------------------------------------------------------------|--|--|--|

| $AV_{DD}$        | AVDD                                                         | Power supply for analogue circuits                                  |  |  |  |

| $DV_{DD}$        | DVDD                                                         | Power supply for digital circuits                                   |  |  |  |

| $V_{DEC}$        | VDEC                                                         | Power supply for core logic, derived from DVDD by on-chip regulator |  |  |  |

| $V_{BIAS}$       | S VBIAS Internal analogue reference level, derived from AVDD |                                                                     |  |  |  |

| AV <sub>SS</sub> | AV <sub>SS</sub> AVSS Ground for all analogue circuits       |                                                                     |  |  |  |

| DV <sub>SS</sub> | DVSS                                                         | Ground for all digital circuits                                     |  |  |  |

Table 1 Definition of Power Supply and Reference Voltages

# 4 Component and PCB Recommendations

# 4.1 Recommended External Components

Figure 2 CMX7241 (L4 and Q3) Recommended External Components

Figure 3 CMX7341 (Q3) Recommended External Components

# **Table 2 Recommended External Components**

| R1  | 100k $\Omega$ | C1  | 18pF     | C11 | not used | C21 | 10nF       |

|-----|---------------|-----|----------|-----|----------|-----|------------|

| R2  | 20k $Ω$       | C2  | 18pF     | C12 | 100pF    | C22 | 10nF       |

| R3  | 20k $Ω$       | C3  | 10nF     | C13 | not used | C23 | 10nF       |

| R4  | 20k $Ω$       | C4  | not used | C14 | 100pF    | C24 | 10μF       |

| R5  | 100k $Ω$      | C5  | 1nF      | C15 | note 5   |     |            |

|     | (note 2)      |     |          |     |          |     |            |

| R6  | 100k $\Omega$ | C6  | 100pF    | C16 | 200pF    |     |            |

| R7  | 100k $Ω$      | C7  | 1μF      | C17 | 10μF     |     |            |

|     | (note 3)      |     |          |     |          |     |            |

| R8  | 100k $\Omega$ | C8  | 100pF    | C18 | 10nF     | X1  | 19.2MHz    |

| R9  | See note 4    | C9  | 100pF    | C19 | 10nF     |     | See note 1 |

| R10 | 100k $\Omega$ | C10 | not used | C20 | 10uF     |     |            |

| R11 | 100k $\Omega$ |     |              |

|-----|---------------|-----|--------------|

| R12 | 100k $\Omega$ | R20 | 47k $\Omega$ |

| R13 | 100k $\Omega$ | R21 | 47k $\Omega$ |

| R14 | 100kO         |     |              |

Resistors  $\pm 5\%$ , capacitors and inductors  $\pm 20\%$  unless otherwise stated.

#### Notes:

- 1. X1 can be a crystal or an external clock generator; this will depend on the application. The tracks between the crystal and the device pins should be as short as possible to achieve maximum stability and best start up performance. By default, a 19.2MHz oscillator is assumed (in which case C1 and C2 are not required), other values could be used if the various internal clock dividers are set to appropriate values.

- 2. For CMX7241 operation, R5 should be selected to provide the desired dc gain of the discriminator input, as follows:

$$|GAIN_{DISC}| = 100k\Omega / R5$$

The gain should be such that the resultant output at the DISCFB pin is within the DISC input signal range specified in 6.15.2. For C4FM modulation, this signal should be dc coupled from the Limiter/ Discriminator output.

3. For CMX7241 operation, R7 should be selected to provide the desired dc gain of the alternative input as follows:

$$|\mathsf{GAIN}_{\mathsf{AIT}}| = 100 \mathrm{k}\Omega / \mathrm{R7}$$

The gain should be such that the resultant output at the ALTFB pin is within the alternative input signal range specified in 6.15.

4. R9 should be selected to provide the desired dc gain (assuming C15 is not present) of the microphone input as follows:

$$|GAIN_{MIC}| = 100k\Omega / R9$$

The gain should be such that the resultant output at the MICFB pin is within the microphone input signal range specified in 6.15.1. For optimum performance with low signal microphones, an additional external gain stage may be required.

5. C15 should be selected to maintain the lower frequency roll-off of the MIC input as follows:

$$C15 \ge 30nF \times |GAIN_{MIC}|$$

- 6. When used with a Limiter/Discriminator Receiver, ALT and ALTFB connections allow the user to have a second discriminator or microphone input. Component connections and values are as for the respective DISC and MIC networks. If this input is not required, the ALT pin should be connected to AVss.

- 7. AUDIO output is used when SPI-Codec or Analogue mode has been selected.

- 8. A single 10µF electrolytic capacitor (C24, fitted as shown) may be used for smoothing the power supply to both VDEC pins, providing they are connected together on the pcb with an adequate width power supply trace. Alternatively, separate smoothing capacitors should be connected to each VDEC pin. High frequency decoupling capacitors (C3 and C23) must always be fitted as close as possible to both VDEC pins.

- 9. TXENA and RXENA should be pulled down by an external resistor (R20, R21) to be directly compatible with the CMX994 (active high signals). For compatibility with earlier 7141-based FI operation, they should be pulled high (active low signals).

# 4.2 PCB Layout Guidelines and Power Supply Decoupling

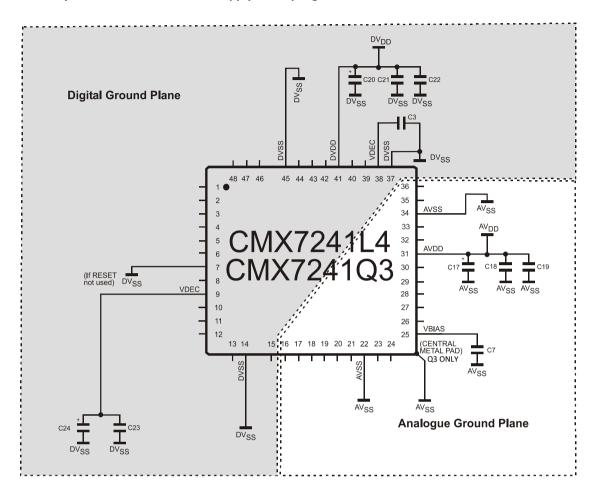

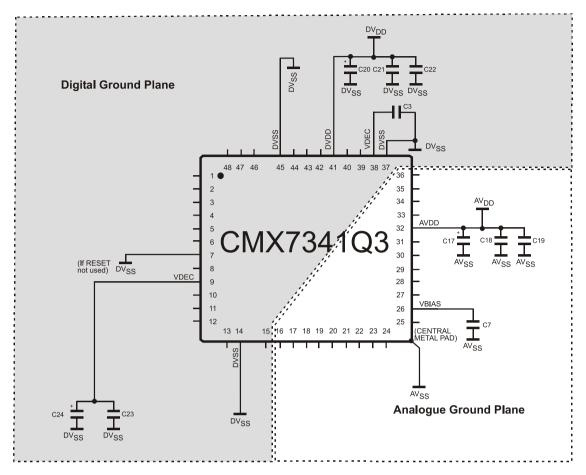

Figure 4 CMX7241 (L4/Q3) Power Supply and Decoupling

Component Values as per Figure 2

Figure 5 CMX7341 (Q3) Power Supply and De-coupling

Component Values as per Figure 3

#### Notes:

- 1. It is important to protect the analogue pins from extraneous in-band noise and to minimise the impedance between the CMX7241/7341 and the supply and bias de-coupling capacitors. The de-coupling capacitors C3, C7, C18, C19, C21, C22 and C24 should be as close as possible to the CMX7241/7341. It is therefore recommended that the printed circuit board is laid out with separate ground planes for the AVSS and DVSS supplies in the area of the device, with provision to make links between them, close to the device. Use of a multi-layer printed circuit board will facilitate the provision of ground planes on separate layers.

- VBIAS is used as an internal reference for detecting and generating the various analogue signals. It must be carefully decoupled, to ensure its integrity, so apart from the decoupling capacitor shown, no other loads should be connected. If VBIAS needs to be used elsewhere in the design, it should be buffered with a high input impedance buffer.

- 3. The single ended microphone input and audio output must be ac coupled (as shown), so that their return paths can be connected to AVSS without introducing dc offsets. Further buffering of the audio output is advised.

- 4. The crystal, X1. may be replaced with an external clock source.

- 5. The device executes an internal scheduler running at 4kHz, which may result in current "spikes" on the DVDD line, which must be taken into account when designing the power supply circuitry.

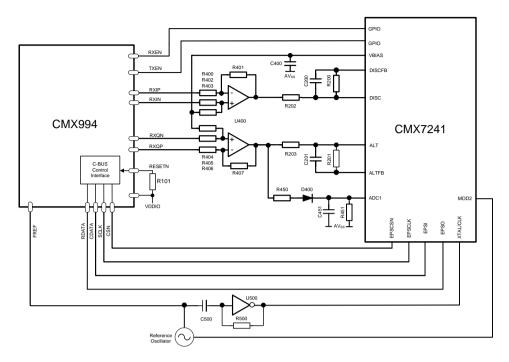

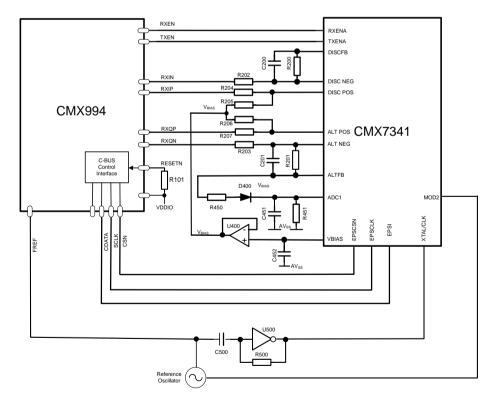

#### 4.3 CMX994/CMX994A/CMX994E Interface

When operating the CMX7241 and CMX7341 in I/Q mode, the interface to the CMX994 shown in Figure 6 and Figure 7 respectively should be used. Component values are shown in Table 3. Where values are not shown refer to the CMX994/A/E Datasheet. The CMX7341 allows for a differential interface directly to the CMX994. Resistors R20 and R21 are required to ensure that the TXENA and RXENA signals are kept in an inactive state during FI loading, and to inform the FI that these signals should be implemented active high.

The CMX994 and the CMX7341 may share the same 19.2MHz reference (however note that the CMX7341 requires a CMOS logic compatible signal).

AuxADC1 is configured to sense the Adjacent/Alternate channel power levels and so improve the performance of the CMX994 AGC system in situations where high levels of interference may be encountered. The CMX994 should be connected to the Auxilliary SPI/C-BUS using EPCSN as the chip select.

Figure 6 CMX7241/CMX994 Interface

Figure 7 CMX7341/CMX994 Interface

| R101         | 100k $Ω$    | C200 | 100pF | D400 | MMBD1503A           |

|--------------|-------------|------|-------|------|---------------------|

| R200 to R207 | 100k $Ω$    | C201 | 100pF | U400 | e.g. LMV931MG       |

| R450         | $22k\Omega$ | C400 | 100nF | U500 | e.g. SN74AHC1G04DRL |

| R451         | $1M\Omega$  | C451 | 1nF   |      |                     |

| R500         | 100k $Ω$    | C452 | 100nF |      |                     |

|              |             | C500 | 1nF   |      |                     |

Table 3 Recommended External Components when using CMX994

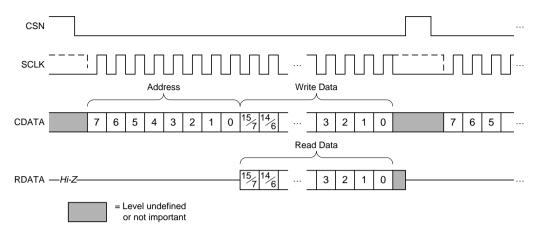

# 4.4 Serial Port Interfaces

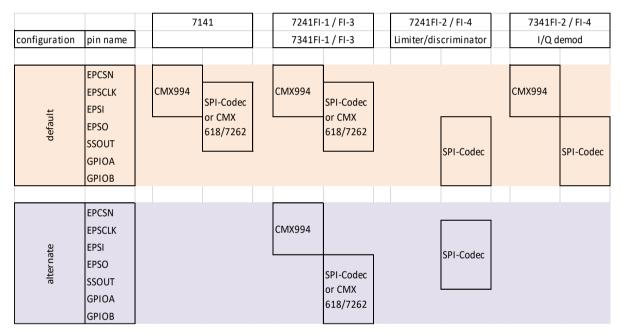

Two serial ports are available on the device to interface to a CMX994 and provide an audio SPI-codec interface. On the 7241FI-1 and 7241FI-3 these can be multiplexed together (with separate CSN signals) or entirely separate, whilst on the 7241/7341FI-2 and 7241/7341FI-4 they must be kept separate. Further information is available in sections 5.6.1 and 5.6.2.

Table 4 shows the options available and includes the CMX7141 to show where backwards compatibility is feasible.

**Table 4 Serial Port Assignments**

#### 4.5 RESET Pin

This pin (pin 7) provides a dedicated reset function when connected to a suitable host microprocessor. To use reset the pin must be held high for a minimum of 100ns and then released. When the state of reset changes from 1 to 0, the same effect as a power-on reset is achieved.

# 5 General Description

## 5.1 7241/7341FI-4 Features

The 7241/7341FI-4.x Function Image™ is intended for use in half duplex digital APCO P25 equipment using C4FM modulation at 9.6kbps in 12.5kHz channels, and analogue FM using 12.5/25kHz channels. Analogue and Digital modes may be enabled simultaneously, allowing automatic detection of the signal type on the RF channel. A flexible power control facility allows the device to be placed in its optimum powersave mode when not actively processing signals.

The device includes a crystal clock generator, with buffered output, to provide a common system clock if required. A block diagram of the device is shown in Figure 1. The signal processing blocks can be routed from any of the three DISC/ALT/MIC input pins.

#### 5.2 Digital Features

Much of the APCO P25 standard Air Interface physical layer protocol is embedded in the 7241/7341FI-4.x Function Image™ operation namely:

- C4FM modulation and demodulation

- Bit and symbol definition

- Frequency and symbol synchronisation

- Transmission burst building and splitting

## 5.3 Analogue Features

The device provides full audio/voice processing to suit the requirements of EN 300 086 and TIA 603D as well as comprehensive signalling to suit professional radio environments:

- Selectable pre-emphasis and de-emphasis

- Selectable voice compander

- Selectable frequency inversion scrambling

- Tx limiter and splatter filter

- Mic AGC

- Selectable sub-audio rejection filter

- CTCSS and DCS generator and decoder (including phase reversal detection)

- Support for external CTCSS/DCS generation and decoding with selectable filters

- 1200/2400 bps FFSK modem for MPT1327

- ADSW and CCSW reporting in MPT1327 mode

- 16-tone Selcall generator and decoder

- DTMF generator and decoder

- Tone generator

# 5.4 Auxiliary Functions

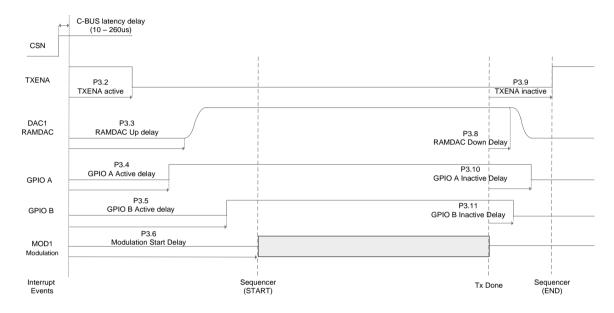

- Automatic Tx sequencer simplifies host control

- RAMDAC operation

- TXENA and RXENA hardware signals

- Two-point or I/Q modulation outputs

- Hard or soft data output options

- Two programmable system clock outputs

- Two auxiliary ADCs with four selectable external input paths

- Four auxiliary DACs, one with built-in programmable RAMDAC

#### 5.5 Interface

- Optimised C-BUS (4-wire, high-speed synchronous serial command/data bus) interface to host for control and data transfer

- Open drain IRQ to host

- Auxiliary SPI/C-BUS interface to CMX994 with pass-through mode from host

- Auxiliary SPI-Codec bus interface for PCM speech codec to support third-party vocoders, e.g. IMBE

- Two GPIO pins

- C-BUS (host) boot mode.

#### 5.6 System Design

#### 5.6.1 General

The device can support two RF receiver architectures:

- Limiter/Discriminator or

- I/Q using the CMX994 Direct Conversion Receiver

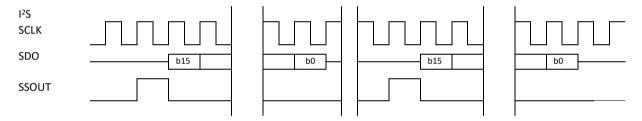

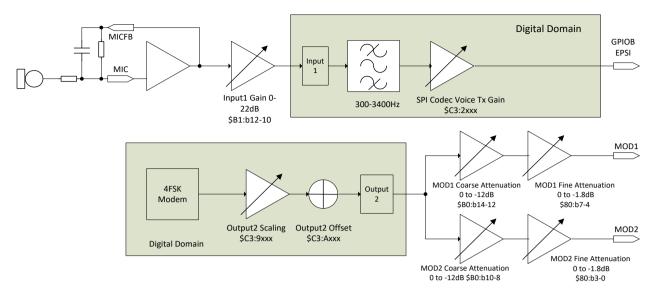

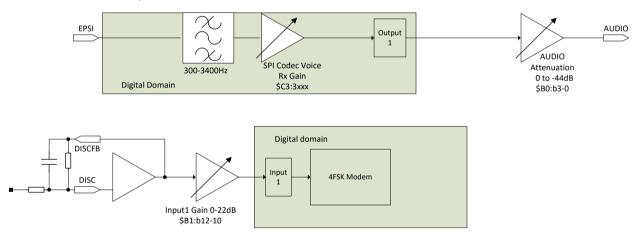

The configuration of the auxiliary SPI/C-BUS port is controlled by the Program Register P6.1: b3-0. In SPI-Codec mode 16-bit PCM audio samples are transferred at 8ksps. When this mode is selected:

**in Tx:** the MIC input should be routed from MIC to Input1. The input signal is lowpass filtered, converted to 16-bit linear PCM at 8ksps and then output on the EPSI pin of the SPI-Codec port for the external vocoder to process.

**in Rx:** the AUDIO output should be routed from Output1. 16-bit linear PCM samples are read from the EPSO pin of the SPI-Codec port, then filtered and output via the Audio Output Attenuator. This mode can also be used for voice annunciations/warnings etc.

#### 5.6.2 Third-party Vocoder Support

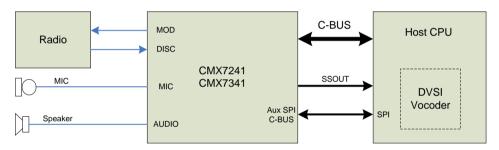

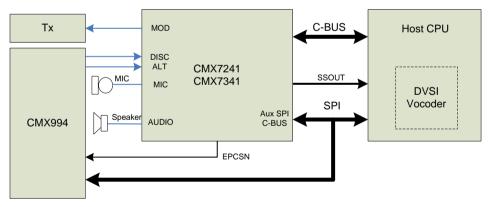

It is possible to use a third-party vocoder by routing all payload data (including voice traffic channel data) through the main C-BUS to the host. The host can then transfer it to/from the third party vocoder over a suitable port supported by the chosen vocoder. Typically these vocoders do not include audio Digital-to-Analogue and Analogue-to-Digital converters, so the device can be configured to use the auxiliary C-BUS as an SPI interface and use its built-in DAC/ADCs as audio converters to accept or deliver PCM audio samples. This architecture is shown in Figure 8 and Figure 9. See also section 6.4. Note that the vocoder functionality could be provided by the host micro in this mode.

Figure 8 DVSI Vocoder Connection

Figure 9 CMX994 and DVSI Connection

## 5.6.3 Data Transfer

When transmitting, an initial block of payload or control channel data will need to be loaded from the host into the C-BUS Tx FIFO. The device can then transmit that data while at the same time loading in the following data blocks from the host or vocoder.

When receiving, the host needs to consider that when a signal is received over the air there will be a processing delay while the device filters and demodulates the output data before presenting it to the host or vocoder. For best performance, voice payload data can be output in soft-decision (4-bit log-likelihood ratio) format compatible with third-party vocoders, although this mode increases the data transfer rate over C-BUS by a factor of four.

## 5.6.4 CMX994 Connection (I/Q Mode)

The CMX994 can be connected via the C-BUS connection in place of the serial memory (Table 5).. This allows the CMX994 to be used along with a DVSI vocoder or other third party vocoder.

| CMX7241/7341 Pin | CMX994 Pin |

|------------------|------------|

| EPCSN            | CSN        |

| EPSI             | CDATA      |

| EPSCLK           | SCLK       |

| No connection    | RDATA      |

Table 5 CMX994 Connections

The operation of the CMX994 is generally automatic, however specific data may be written to CMX994 registers using the pass-through mode available using register \$C8. For example if the CMX994 PLL and VCO are used in the radio design then it is necessary to programme the appropriate frequency data to the CMX994 PLL-M Divider, PLL N-Divider and VCO Control registers using the pass-through mode before attempting reception.

The CMX994A/CMX994E devices are pin compatible with CMX994 and may be used instead. In order to make use of the advanced features Program Block P6.2 should be set appropriately.

#### CMX994 Rx Control: \$12

| Bit: | 7       | 6      | 5       | 4        | 3        | 2        | 1    | 0    |

|------|---------|--------|---------|----------|----------|----------|------|------|

|      | Mix Pwr | IQ Pwr | LNA Pwr | ACR Flt2 | ACR Flt1 | DC Range | DIV2 | DIV1 |

#### CMX994 Rx Offset: \$13

| Bit: | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------|------|------|------|------|------|------|------|------|

|      | QDC3 | QDC2 | QDC1 | QDC0 | IDC3 | IDC2 | IDC1 | IDC0 |

#### CMX994 Rx Gain: \$16

| Bit: | 7   | 6   | 5         | 4         | 3                  | 2  | 1  | 0  |

|------|-----|-----|-----------|-----------|--------------------|----|----|----|

|      | GS1 | GS0 | LNA Gain2 | LNA Gain1 | LNA Z <sub>0</sub> | G2 | G1 | G0 |

Yellow indicates CMX994 C-BUS bit fields that are controlled by 7x41 Fl. All other registers and bit fields should be set up appropriately by the host using the pass-through write mode.

## 5.6.5 Hardware AGC – AuxADC1 Connection

In I/Q mode the AuxADC1 input can be used to improve the adjacent/alternate channel rejection with the addition of suitable external components (shown in Figure 6). This function provides a broadband signal detector which is used in the AGC process. This is required to prevent the DISC/ALT ADC inputs limiting internally in the presence of strong alternate channel signals, which are attenuated by the inherent filtering of the ADC.

This functionality is enabled by setting:

- Program Block P6.0:b3=1 (enable hardware AGC)

- \$C0:b6 = 1 (enable BIAS)

- \$93 = \$xx3C (AuxADC1 Enabled, averaging = 3, Routed from AuxADC input 1)

- \$95 = \$0185 (hi threshold)

- \$94 = \$0180 (lo threshold)

Note that threshold levels may need adjustment to suit particular hardware implementations.

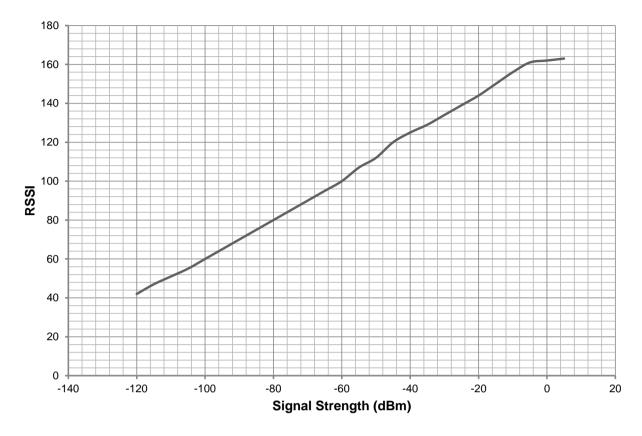

#### 5.6.6 RSSI Measurement (I/Q Mode)

In I/Q mode the RSSI is calculated from the signal levels present at the I and Q inputs and the AGC levels currently in use. Figure 10 shows a typical response.

Figure 10 RSSI in I/Q Mode

# 5.6.7 RSSI Measurement (LD mode)

The AuxADC provided by the device can be used to detect the Squelch or RSSI signal from the RF section while the device is in Rx or Idle mode. This allows a significant degree of powersaving within the device and avoids the need to wake the host up unnecessarily. The host-programmable AuxADC thresholds allow for user selection of squelch threshold settings.

#### 5.7 C4FM Modem

This modem can run at 9.6 kbps occupying a 12.5 kHz bandwidth RF channel. It has been designed such that, when combined with suitable RF, host controller, Vocoder and appropriate control software, it meets the requirements of the APCO P25 standard. See https://www.apcointl.org/ for details of the standard.

## 5.7.1 Modulation

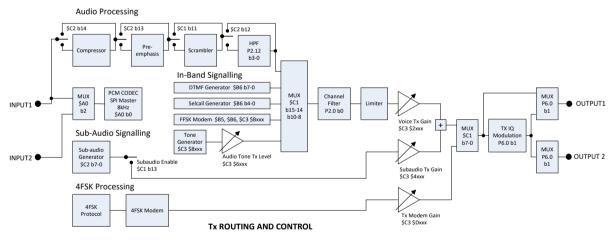

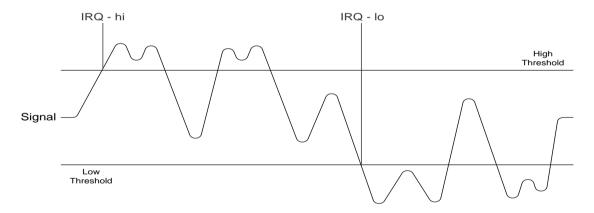

The C4FM modulation scheme operates in a 12.5 kHz channel bandwidth an over-air bit rate of 9.6 kbps (4.8 ksymbols/s). RC filters are implemented in Tx with a filter 'alpha' of 0.2. Figure 13 shows the basic parameters of the C4FM modulation, symbol mapping and filtering requirements. Figure 11 and Figure 12 show a transmitted PRBS waveform, as recorded on a spectrum analyser in 36kHz span and zero-span mode, having been two-point modulated using a suitable RF transmitter.

To follow

Figure 11 C4FM PRBS Waveform (Eye Diagram)

To follow

Figure 12 C4FM Modulation Performance

Inputs to the 4-level encoder are converted to symbol values as follows:

| Di bit | Symbol | Deviation |

|--------|--------|-----------|

| 01     | +3     | +1.8kHz   |

| 00     | +1     | +0.6kHz   |

| 10     | -1     | -0.6kHz   |

| 00     | -3     | -1.8kHz   |

**Table 6 Modulation Deviation**

The symbol input to the Raised Cosine filter is a series of digital "impulses" as described in TIA/EIA-102.BAA paragraph 9.3.

The Raised Cosine filter has alpha = 0.2 and has a frequency response as follows:

$$H(f) = \begin{cases} 1 & \text{for } f < 1920Hz \\ 0.5 + 0.5 \bullet \cos\left(2 \bullet \pi \bullet \frac{f}{1920}\right) & \text{for } 1920 < f < 2880Hz \\ 0 & \text{for } f > 2880Hz \end{cases}$$

The shaping filter has a linear phase frequency response as follows:

$$\begin{cases} \frac{\pi \cdot \frac{f}{4800}}{\sin\left(\pi \cdot \frac{f}{4800}\right)} & \text{for } |f| < 2880Hz \\ \frac{\pi \cdot \frac{f}{4800}}{\sin\left(\pi \cdot \frac{f}{4800}\right)} & \text{for } 2880 \le |f| \le 3500Hz \\ 0 & \text{for } |f| > 3500Hz \end{cases}$$

Figure 13 C4FM Modulation Characteristics

#### 5.7.2 Internal Data Processing

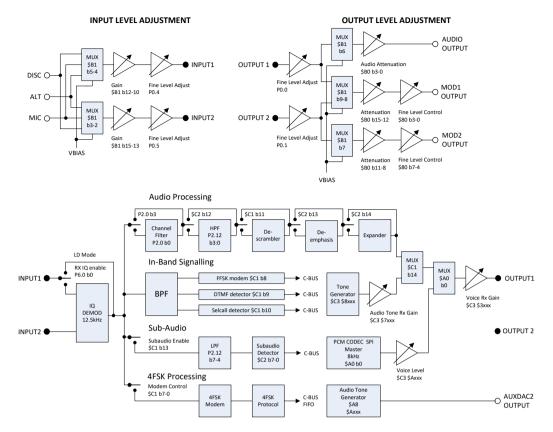

The device operates as a half-duplex device, either receiving signals from the RF circuits in Rx mode, or sourcing signals to the RF circuits in Tx mode. It also has a low power Idle mode to support battery saving protocols. The internal data processing blocks for Tx and Rx modes are illustrated in Figure 14.

Figure 14 Internal C4FM Data Processing Blocks

Figure 15 Additional Internal Data Processing in I/Q Mode

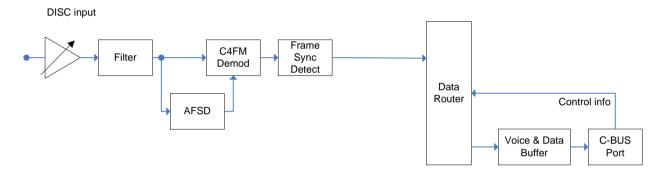

# 5.7.3 Frame Sync Detection and Demodulation

The analogue signal from the receiver may be from either a CMX994 I/Q interface or a limiter/discriminator (LD) output. The signal(s) from the RF section should be applied to the CMX7241/7341 input(s) (normally the DISC input for LD Rx and DISC and ALT inputs for I/Q Rx). The signals can be adjusted to the correct level either by selection of the feedback

resistor(s) or using the CMX7241/7341 Input Gain settings. In LD mode the signal is filtered using an Integrate-and-Dump filter matching the filters applied in the transmitter, then passed to the AFSD (Automated Frame Sync Detector) block which extracts symbol and frame synchronisation. During this process the C4FM demodulator and the data-processing sections that follow are dormant to minimise power consumption. When frame synchronisation has been achieved, the AFSD section is powered down and timing and symbol-level information is passed to the C4FM demodulator, which starts decoding the subsequent data bits.

In I/Q mode filtering is applied to the input signals and dc offsets are removed before an inverse tan function performs the FM demodulation function. The output of this stage has an offset depending on the frequency error of the received signal compared to the nominal frequency of the receiver. This offset is removed before filtering, after which the signal chain is then the same as the LD case. In I/Q mode the CMX7241/7341 provides measurements of frequency error and RSSI (which are not available in LD mode).

A C4FM burst begins with an optional preamble sequence followed by a 48-bit frame sync. The CMX7241/7341 uses the frame sync to detect the start of a transmission. Frame sync detects are reported with an FS Detect IRQ and a code in the C4FM Modem Status register (\$C9). When frame synchronisation has been achieved, the C4FM demodulator is enabled, frame sync detection is switched off and subsequent frame sync sequences embedded in the received frames are not reported.

#### 5.7.4 Voice Coding

The CMX7241/7341 can support any third-party vocoder by routing voice payload data over the main C-BUS interface and through the host. In this mode, all vocoder control and data transfers must be managed by the host. Voice data transferred to the host may use either hard decision bits or soft decision (4-bit log-likelihood ratio) format. Using soft decision format increases the required data transfer rate over C-BUS by a factor of four.

#### 5.7.5 Radio Performance Requirements

For optimum performance, the signal should not be significantly degraded by filters that are excessively narrow and/or cause significant group delay distortion. Care should be taken in interfacing the device to the radio circuits to maintain the frequency and phase response (both low and high end), in order to achieve optimum performance. Test modes are provided to assist in both the initial design and production set-up procedures. Further information and application notes can be found at http://www.cmlmicro.com.

# 5.8 Audio/Voice Functions

#### 5.8.1 Microphone